Novo chip da UC San Diego promete reduzir desperdício energético em data centers

Pesquisadores da Universidade da Califórnia em San Diego (UC San Diego) desenvolveram um novo chip que pode revolucionar a eficiência energética dos data centers, especialmente no que diz respeito à alimentação das unidades de processamento gráfico (GPUs). A inovação consiste em repensar o modo como a energia elétrica é convertida para alimentar esses componentes, utilizando uma combinação inédita de elementos piezoelétricos vibratórios e um layout de circuito inteligente.

Desafios da conversão de energia em data centers

Data centers modernos distribuem energia tipicamente em tensões elevadas, como 48 volts, enquanto GPUs exigem tensões muito mais baixas, na faixa de 1 a 5 volts. O desafio está em converter essa alta tensão para níveis seguros e eficientes, minimizando perdas de energia e garantindo fornecimento suficiente de corrente. Os conversores DC-DC step-down convencionais, que fazem essa redução, geralmente utilizam componentes magnéticos como indutores, que já atingiram limites práticos de eficiência e miniaturização.

Inovação com ressonadores piezoelétricos híbridos

O time liderado pelo professor Patrick Mercier explorou uma abordagem alternativa utilizando ressonadores piezoelétricos, que armazenam e transferem energia por meio de vibrações mecânicas ao invés de campos magnéticos. Esses componentes têm potencial para ser menores, mais densos em energia e mais fáceis de fabricar em escala, mas versões anteriores enfrentavam dificuldades para manter eficiência e potência em grandes quedas de tensão.

Para superar essas limitações, os pesquisadores criaram um conversor híbrido que combina o ressonador piezoelétrico com capacitores comerciais dispostos em uma configuração cuidadosamente projetada. Esse arranjo permite que o sistema lide melhor com grandes conversões de tensão, abrindo múltiplos caminhos para o fluxo de energia, reduzindo perdas e o estresse sobre o ressonador.

Resultados do protótipo e eficiência alcançada

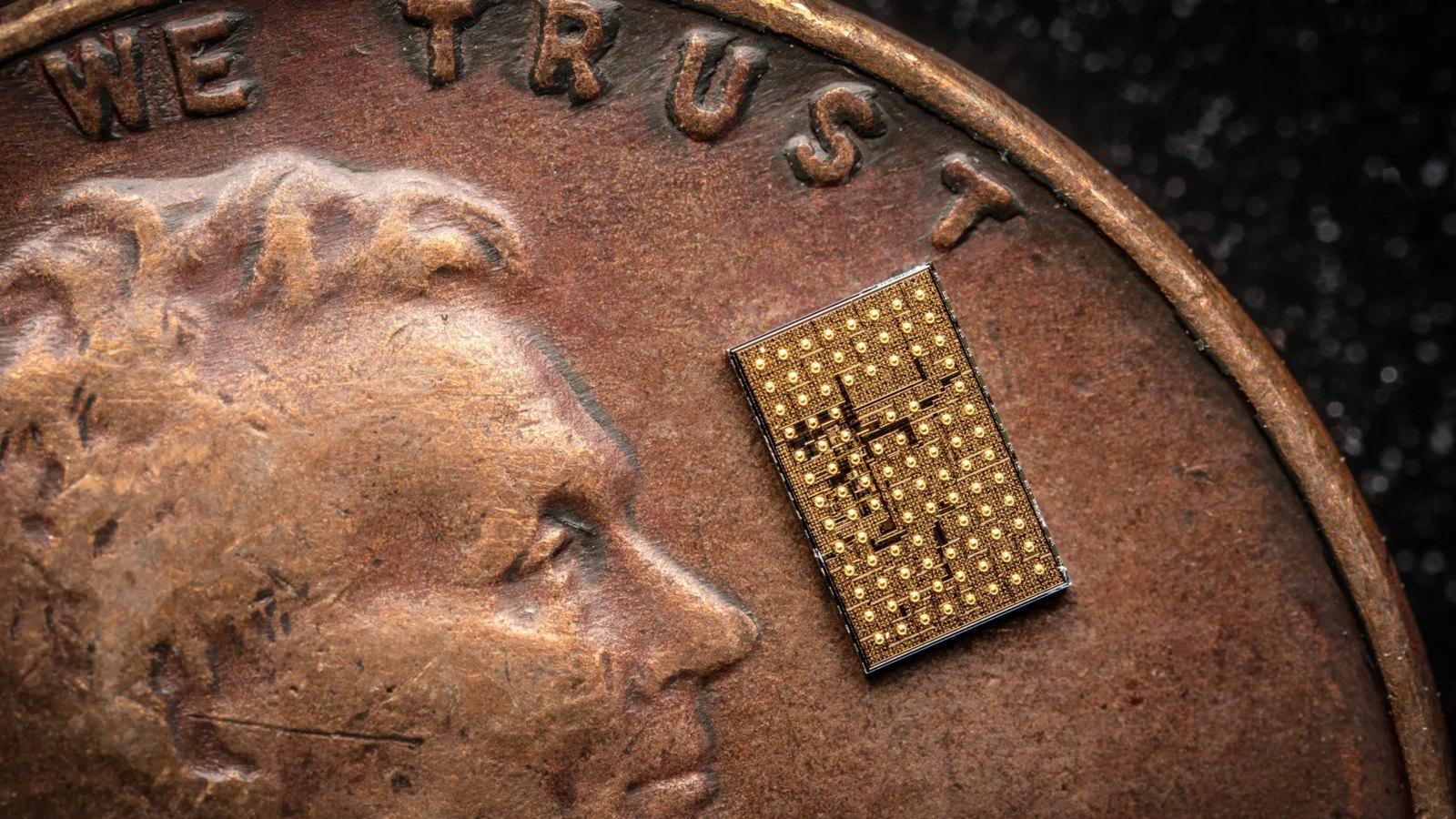

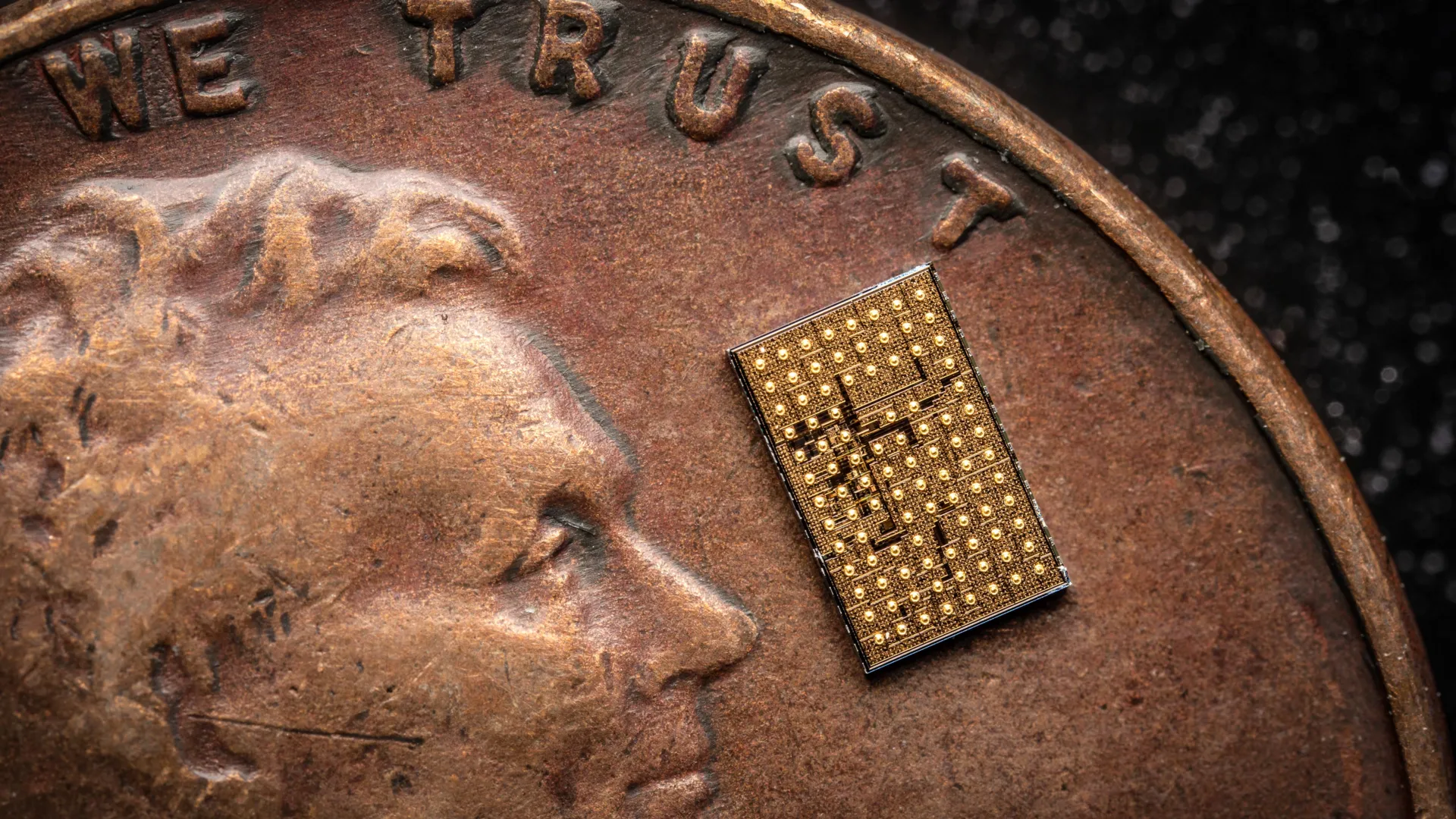

O protótipo do chip desenvolvido foi testado em laboratório e conseguiu converter 48 volts para 4,8 volts com uma eficiência máxima de 96,2%, nível bastante elevado para essa faixa de tensão. Além disso, entregou aproximadamente quatro vezes mais corrente de saída do que designs piezoelétricos anteriores, demonstrando avanços significativos em potência e eficiência.

Implicações e próximos passos para aplicação prática

Apesar do sucesso inicial, a tecnologia ainda está em fase de desenvolvimento. Um dos desafios técnicos é a integração dos ressonadores piezoelétricos, que vibram fisicamente e não podem ser soldados diretamente em placas de circuito com as técnicas tradicionais. Isso demanda novas estratégias de embalagem e montagem para viabilizar o uso em data centers reais.

Os pesquisadores planejam continuar aprimorando os materiais, o design dos circuitos e os métodos de embalagem, visando tornar o chip pronto para uso comercial. A expectativa é que, no futuro, essa tecnologia contribua para sistemas de computação de alto desempenho mais compactos e energeticamente eficientes, reduzindo o impacto ambiental dos data centers.